Recently Blue Pearl Software announced the availability of a new feature named ACE – Advanced Clock Environment (http://www.bluepearlsoftware.com/ace/ ). We at VerifWorks tried it on one of our existing DSP designs.

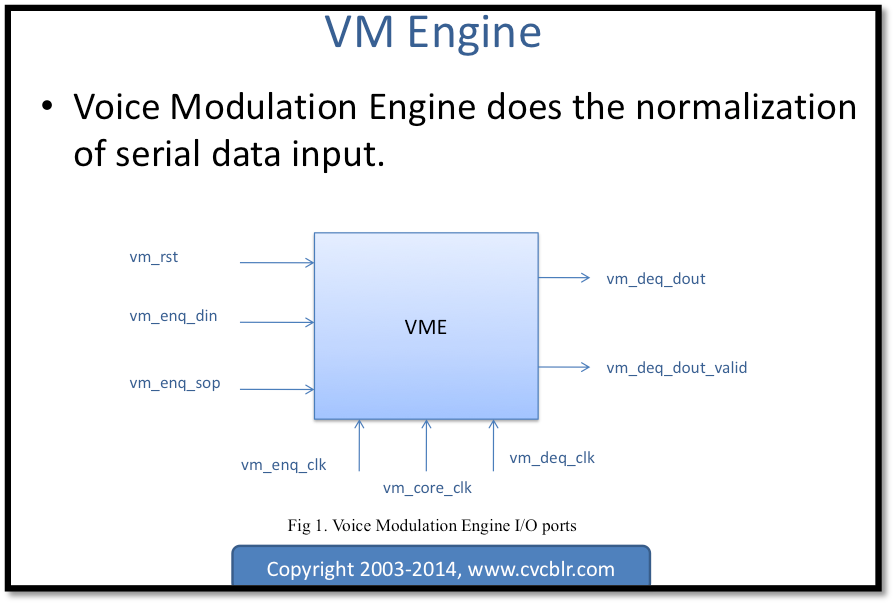

The design is not very complex, but it has multiple clock domains, as the core clock is faster than the Enqueue and Dequeue logic.

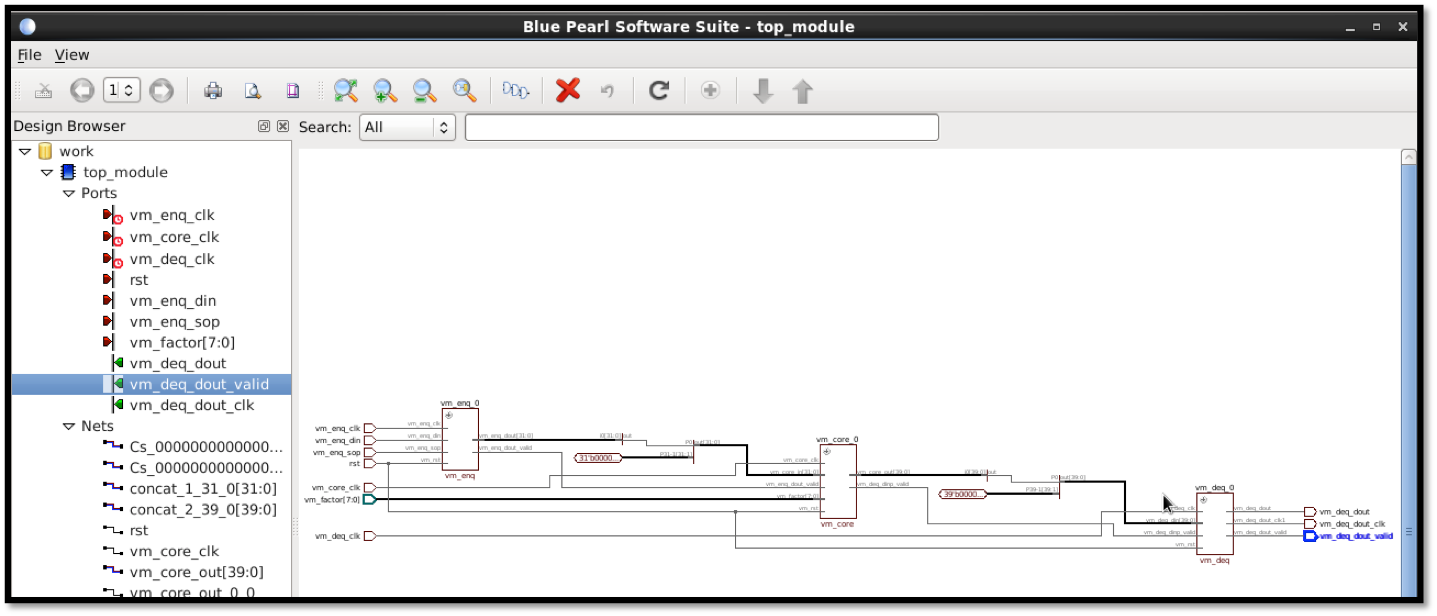

It is pure Verilog RTL and reading it into Blue Pearl tool went very smooth. In matter of seconds we got a schematic as below:

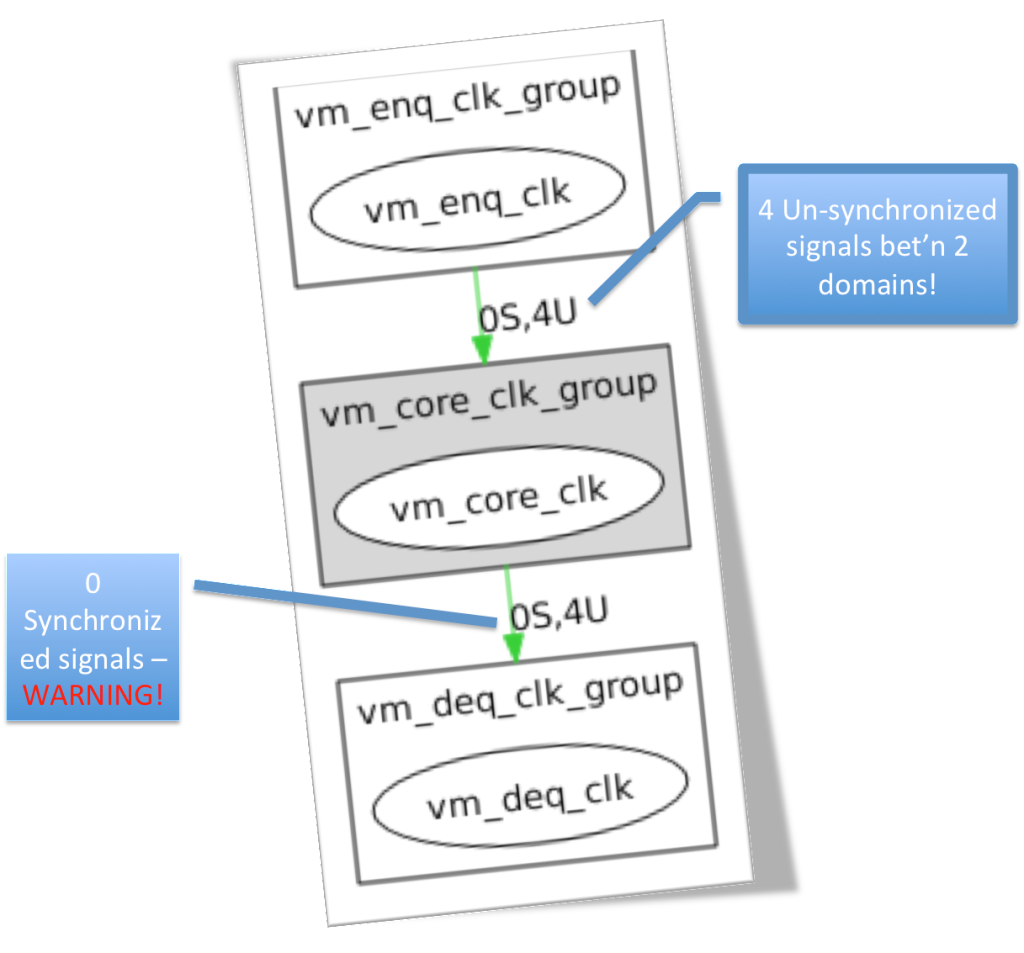

All looked fine, a new icon launches the ACE feature – aptly abbreviated as “ACE – Advanced Clock Environment”, it abstracts all the logic, connections, wires down to pure “clock domains”, see below:

As can be seen in the picture above, the tool makes several recommendations, reports findings in brief such as:

- Number of clocks found

- Number of clock domains identified (this could be tweaked by the designer/micro-architect visually in the tool if needed)

- Number of signals in the landing/destination domain that are Synchronized and Unsynchronized etc.

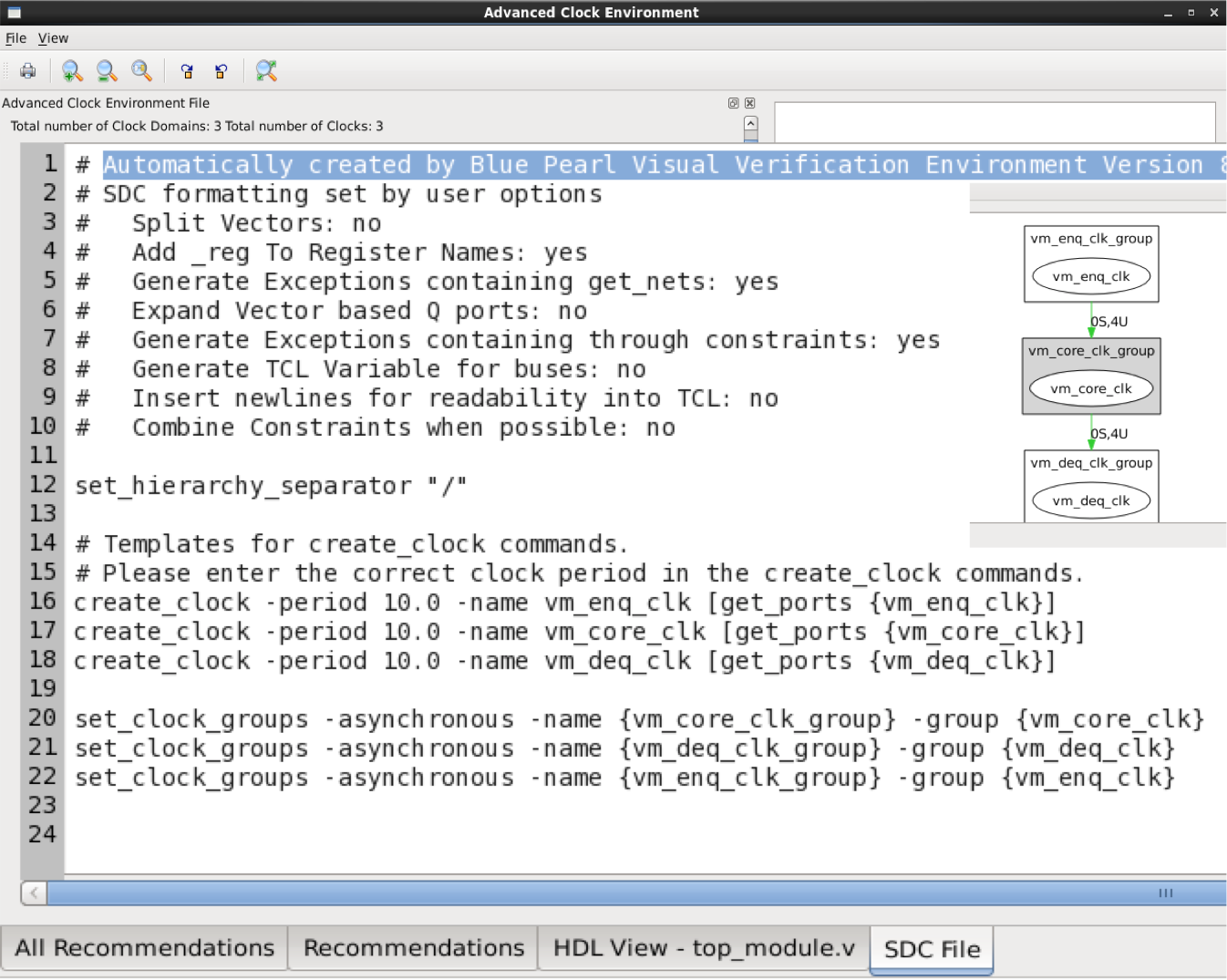

That’s a handful of neat, quick “health” checks on your design with click of a button! It doesn’t stop there; one can generate a SDC (Synopsys Design Constraints) file containing the clock domains. It is part of the GUI, available as an extra tab as shown below.

One can do more analysis, tweak the SDC file, re-feed to the tool for further analysis etc. We hope to over them in upcoming blog articles. Meanwhile you can try this amazingly simple to use tool in your flow right away – it is FREE for 30 days, see: http://goo.gl/CCp0SQ

Pingback: FPGA Verification done the smart way - the Bluepearl way! - Verification News Portal - ASIC & FPGA