Recently a smart engineer at Maxim Integrated Circuits asked a tricky question on operator ordering/precedence in an online UVM forum. Though the question originated from UVM/TB code, the similar situation could easily occur in RTL design. Here is a code snippet:

Does SystemVerilog standard specify the order in which logical and bit-wise operations get executed, or is it a tool dependent issue?

An example:

if (x & y == z) does this mean:

– if ((x&y) == z) or

– if (x & (y ==z))

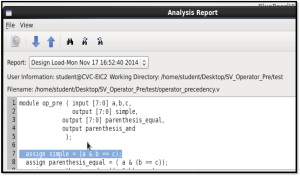

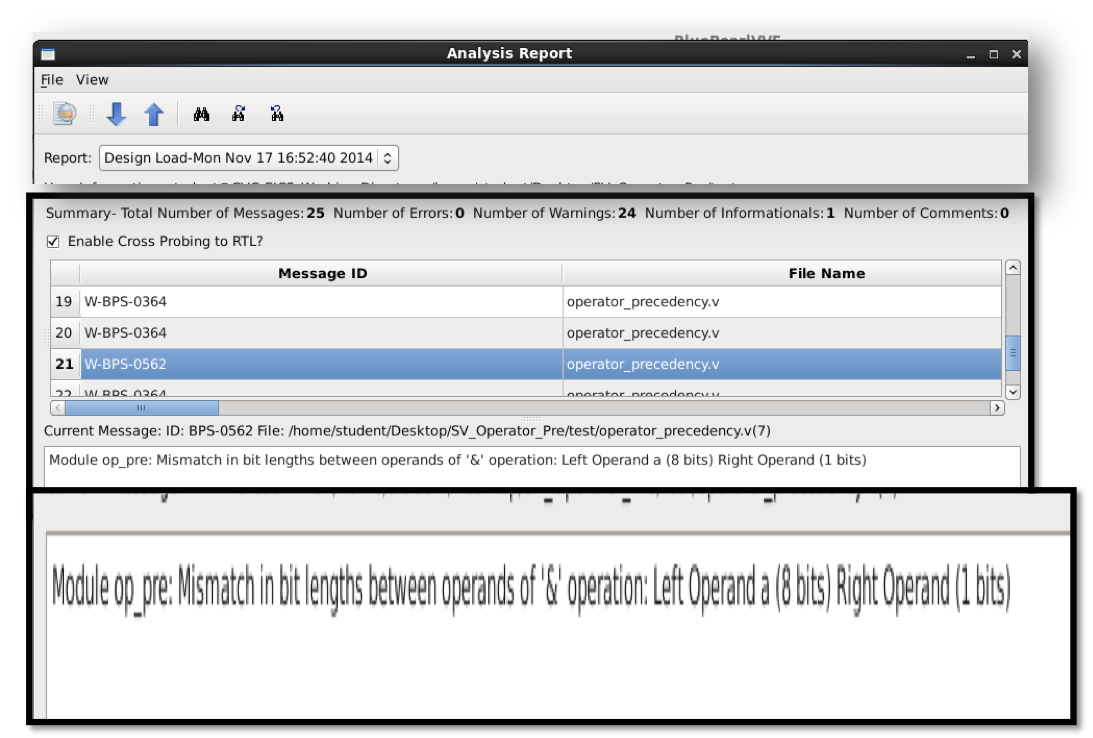

As our CTO, Srini responded online, the ordering is indeed well defined, with ” == ” having higher precedence. However it is also quite important to note that the bitwise/binary AND-ing in the code example is performed among operands of varying bit lengths/sizes. This can be a serious concern and might lead to design errors/unwanted behaviors. When we ran Bluepearl’s advanced “Analysis” engine on the above, it quickly highlighted the same (in less than 30 seconds infact), see below:

Given the speed and accuracy with which BPS (BluePearl Software) Analysis runs, it is no brainer that investing in a tool as handy as this could save many hours of debug for the end users. Incase you want to try your hands on this simple, yet powerful tool, contact us via info@cvcblr.com and we will be glad to assist you.